ESD system protection overview: Combined with TVS application PCB layout optimization and electromagnetic compatibility design points

2024-06-26 10:21:44 1484

The success of protecting a system from ESD (electrostatic discharge) is largely dependent on the design quality of the printed circuit board (PCB). While the selection of a suitable transient voltage suppressor (TVS) is fundamental to implementing an ESD protection strategy, it is outside the scope of this article. The selection guide for ESD protection devices can be found in INFINITECH's previous technical documentation, which can help determine the type of TVS diode that suits your specific system needs. Once the right TVS has been selected, designing the PCB layout following the strategies presented in this ESD Layout Guide will be an important path for PCB designers to achieve effective ESD protection.

1. What are the system protection methods to suppress ESD events?

ESD events typically force a current IESD (see Figure 1-1) into the system quickly, either through a user interface (such as a cable connection) or a manual input device (such as a key on a keyboard). Using TVS to protect your system from ESD depends on whether TVS can shunt IESD to the ground. To optimize PCB layout for ESD suppression, it is largely necessary to design an IESD grounding path with the lowest possible impedance. In an ESD event, the voltage VESD provided to the protected integrated circuit (protected IC) is a function of the IESD and the circuit impedance on it. Because designers have no control over IESD, reducing ground impedance is the primary way to minimize VESD.

Reducing impedance requires solving some difficult problems. The main problem is that the impedance cannot be zero, otherwise the protected signal line will short-circuit to the ground. In order to be able to apply the circuit in practice, the protected line needs to be able to maintain a certain voltage, usually with a high impedance to the ground. That's why TVS works.

Figure 1-1. Level 4 (8KV ESD) waveform according to IEC 61000-4-2

TVS is an array of diodes (see Figure 1-2 for a typical example) whose arrangement has an extremely high impedance to the voltage normally present in the circuit, but if the voltage exceeds the design range, the TVS diode will break down and shunt the IESD to ground before the IESD damages the protected system. Therefore, the system designer needs to reduce the impedance against the IESD from the ESD source to the TVS to ground.

Figure 1-2. Typical ESD protection solutions

Figure 1-2. Typical ESD protection solutions

The impedance provided to the IESD is a function of the inherent impedance of the TVS (in the TVS diode array and package) and the PCB layout between the ESD source and the TVS ground. TVS are typically designed to provide the lowest possible ground impedance to IESD as far as their overall design limitations allow. After selecting the appropriate TVS, reducing the impedance between the ESD source and the TVS ground on the PCB layout is a key stage in the design.

Another problem with rapidly changing IESD is that its associated rapidly changing electromagnetic field (EM) can cause interference (EMI) to be coupled to other circuits on the PCB, especially in the area between the ESD source and TVS. Once the TVS shunt the IESD to the ground, the cabling between the TVS and the protected IC should be relatively unaffected by EMI. Therefore, between the ESD source and TVS, the unprotected circuit should not be adjacent to the wiring of the ESD protected circuit. In order to minimize EMI radiation, ideally, the circuit wiring between the ESD source and the TVS should not have a corner of more than 45°, or a curve with a large radius.

In today's PCB layout, layout space is at a premium. Ics, including TVS, must be designed to be very compact. In addition, the placement density of ics on the PCB is also increasing. Multilayer PCB boards and cabling rely heavily on through-holes to maximize density, thereby reducing system size while increasing the system's characteristic Settings. This PCB architecture (especially related to layer switching and through-holes) plays an important role in shunt IESD to ground via TVS. The way the circuit is routed to the TVS using a pass hole can create a large VESD voltage difference on the protected IC. Often, placing an overhole between the ESD source and the TVS has a negative effect, but in some cases, designers have to make this decision. Even in these cases, if done properly, it is still possible to minimize VESD on the protected IC.

Grounding schemes are critical to prevent ESD. Using chassis grounding for TVS (as opposed to digital and/or analog grounding achieved by inductors) is a good way to avoid ESD-related failures. However, this presents a big challenge when wiring high-speed circuits across multiple ground planes. For this reason, many designs use common ground for the protected circuit. The ground plane is essential for TVS to successfully consume IESD without increasing VESD. The electrical connection of the ground grounding case, such as the PCB grounding hole for the case screws, directly adjacent to the TVS grounding and ESD source grounding (for example, connector shielding), provides a reasonable way to keep the ground offset at the protected IC to a minimum. If the system is unable to utilize chassis ground ground, the tightly coupled multi-layer ground plane helps keep ground drift at the protected IC to a minimum.

Summarizing these parameters, the factors that successfully protect a system from ESD include:

• Control the impedance around TVS to consume ESD current IESD

• Limit the impact of EMI on unprotected circuits

• Use the holes correctly to maximize ESD consumption of TVS

• Design an extremely low impedance grounding scheme for TVS

2, PCB layout guidelines for optimizing ESD dissipation

2.1 Optimize impedance to consume ESD

Outside of the controlled RLC values, PCBS have inherent parasitic effects that are beneficial to overall board performance. Often, this parasitic effect is detrimental to the functionality of the design. Inductance is an important parasitic factor to be considered when designing a circuit that consumes ESD. Because (see "Note 1" below) VESD =Vbr_TVS + RDYN(TVS) IESD + L(dIESD/dt), and the term dIESD/dt is very large, the forced current in an ESD event will result in a large voltage drop on any inductor. For example, in the 8kV ESD event specified by IEC 61000-4-2, dIESD/dt = (30A)/(0.8×10^(-9) s) = 4 ×10^ 10A/s. So even a 0.25nH inductance will bring an additional 10V voltage to the system.

Figure 2-1. PCB inductance around single-channel TVS

Figure 2-1. PCB inductance around single-channel TVS

Four parasitic inductors are shown in Figure 2-1: L1 and L2 are the inductors in the circuit between the ESD source (usually a connector) and the TVS, L3 is the inductor between the TVS and the ground terminal, and L4 is the inductor between the TVS and the protected IC.

Without considering the hole, inductors L1 and L4 usually depend on design constraints, such as impedance controlled signal lines. However, by making L4 much larger than L1, IESD can still "pivot" to TVS. This is achieved by placing the TVS close to the ESD source where PCB design rules allow, while keeping the protected IC away from the TVS (for example, near the middle of the PCB). This can effectively produce an L4 >> L1 effect, helping to shunt IESD to TVS. Placing TVS close to the connector also reduces EMI radiated into the system. In a well-designed system, an inductor at L2 should not be present. This indicates that there is a stump between the TVS and the protected line. This design practice should be avoided. The protected line should be connected directly from the ESD source to the TVS pin, ideally with no holes in the path. The inductor at L3 indicates the inductance between the TVS and the ground terminal. This inductance value should be reduced as much as possible and is probably the most dominant parasitic effect affecting VESD.

The voltage provided to the Protected Line node will be VESD = Vbr_TVS + IESD RDYN(TVS) + (L2 + L3)(dIESD/dt). Therefore, PCB designers need to reduce L3 and eliminate L2 as much as possible.

Methods for minimizing L3 are described in Section 2.4. Methods for minimizing L1 are described in sections 2.2 and 2.3.

Brief summary

• Minimize the inductance between the ESD source and the ground path through TVS

• Place TVS near connectors if design rules allow

• Make the distance between the protected IC and TVS far greater than the distance between TVS and connector

• Do not use stumps between TVS and protected lines, wiring directly from ESD source to TVS

• It is important to minimize the inductance between TVS and ground

2.2. Limit EMI caused by ESD

Without proper suppression steps, fast transients like ESD with high di/dt can cause EMI. For ESD, the main radiation source will be located in the circuit between the ESD source and the TVS. Therefore, PCB designers should consider setting this area as an exclusion area for unprotected PCB routing, as it can cause system damage by radiating more EMI through direct contact with the IC or by bringing more EMI into the system. Even if there is no inductance at L1 (as shown in Figure 2-1), the rapidly changing electric field during ESD can be coupled to nearby circuits, creating unwanted voltage on unexpected circuits. Any inductance of L1 will amplify EMI.

Figure 2-2 shows an unprotected line between the ESD source and TVS near the protected line. Such practices should be avoided. In an ESD event, there will be a large dIESD/dt between the ESD source and the TVS. The wiring on this path will radiate EMI, and all nearby wiring will generate a current induced by EMI. If these cabling are not protected by TVS, the induced current in the unprotected line can cause system damage.

If there are any holes in the protected line between the ESD source and the TVS, these principles also apply to any layer through which the hole passes, and the unprotected line should not be near the hole.

Figure 2-2.EMI coupling to adjacent unprotected cabling

Figure 2-2.EMI coupling to adjacent unprotected cabling

Another aspect of PCB layout is to consider the style of the corner between ESD source and TVS. Corners tend to emit EMI during IESD. The best way to route from the ESD source to the TVS is to use the shortest possible straight path. In addition to reducing the impedance in the IESD ground path, shortening the length of this path also reduces the EMI radiated inside the system. If a corner is required, the wiring should be bent at the maximum radius, and if PCB technology does not allow curved wiring, the 45° corner is the maximum Angle.

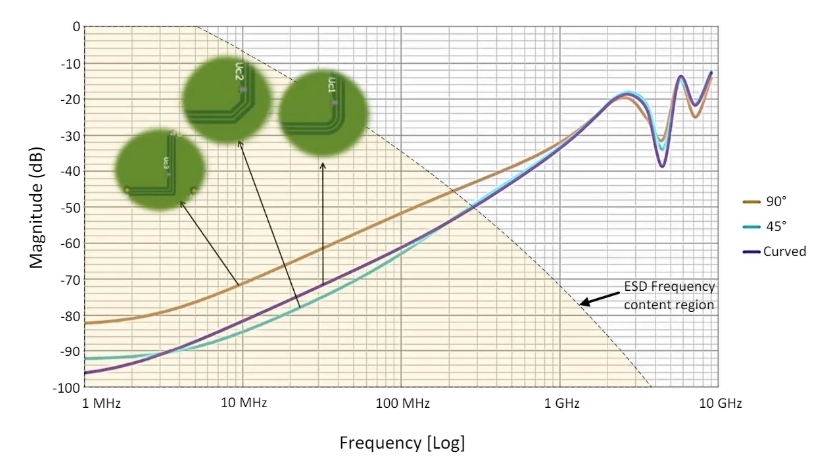

Figure 2-3. Electric fields of three different corner types in an 8KV ESD event

Figure 2-3. Electric fields of three different corner types in an 8KV ESD event

In Figure 2-3, note that for the 90° corner, this corner is a significant source of EMI. The electric field at the corner is at least 7kV. This causes any radius less than 2.6mm (in air) to produce an arc (ionization). The EMI of a 45° curve is less pronounced. To further show the effect of corner styles, Figure 2-4 plots the crosstalk between parallel wiring using these three corner types. The 90° corner has a higher coupling than other corners, especially in the ESD frequency component region.

Figure 2-4. Use crosstalk between cables at 45°, 90°, and curve corners

Figure 2-4. Use crosstalk between cables at 45°, 90°, and curve corners

Brief summary

• Do not place unprotected circuits in the area between the ESD source and TVS.

• Place TVS near connectors if design rules allow.

• If possible, use straight line wiring between ESD source and TVS.

• If corners must be used, curves should be preferred, with a maximum acceptable Angle of 45°.

2.3, through the hole for wiring

It is best to route from the ESD source to the TVS on the PCB without going through the hole switching layer. Figure 2-5 shows two examples. In the first case, there is no hole between the ESD source and the TVS, so the IESD is forced into the TVS protection pin and then through the hole to reach the protected IC. In this case, the hole is represented by L4 (Figure 2-1). In the second case, the IESD branches between the protected IC and the through hole and reaches the TVS protection pin. In this case, the hole is represented by L2 (Figure 2-1). Such practices should be avoided. The inductance through the hole is located between the TVS and the path from the ESD source to the protected IC. This has two adverse effects: Because the current looks for the ground path with the least impedance, the protected IC may be hit by the current in the IESD, and any current passing through the hole will increase the voltage provided to the protected IC.

Figure 2-5. Routing cables through holes

Figure 2-5. Routing cables through holes

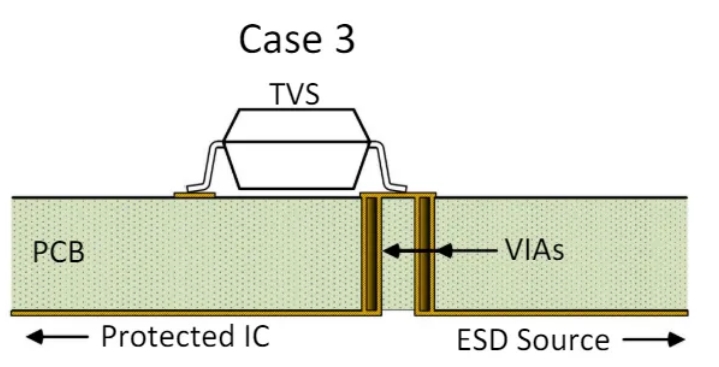

In some cases, designers have no choice but to place TVS on a different layer than the ESD source. Figure 2-6 shows the third case, which is a variation of the second case. In the third case, the IESD is forced into the protection pin of the TVS before the IESD establishes a path with the protected IC. This is an acceptable compromise for the second case.

Figure 2-6. Route cables through holes

Figure 2-6. Route cables through holes

These three cases represent examples of the use of holes between an ESD source and a protected IC. It is best to avoid this practice, but if necessary, the first case is the preferred method, the second case should be avoided, and the third case can be accepted if there is no alternative.

Brief summary

• If possible, avoid passing holes between ESD source and TVS

• If a pass hole is required between the ESD source and the protected IC, route directly from the ESD source to the TVS before using the pass hole

2.4. Optimize ESD grounding scheme

Successful elimination of all parasitic inductance between the ESD source and the TVS will only be effective if the TVS has a ground path with very low inductance. The TVS ground pin shall be connected to a ground plane of the same layer that is coupled to another ground plane on the directly adjacent layer. These ground planes should be spliced together through holes, one of which is next to the ground pin of the TVS (see Figure 2-8).

Figure 2-7 shows the PCB inductance around the single-channel TVS (as shown in Figure 2-1 above). Only inductance at L3 is considered in this section. Note that with L2 eliminated, the voltage provided to the protected IC during an ESD event would be VESD = Vbr_TVS + IESD RDYN(TVS) + L3(dIESD/dt), while at 8kV, dIESD/dt = 4 × 10^10. Obviously, L3 must be reduced as much as possible.

Figure 2-7. PCB inductance around single-channel TVS

Figure 2-7. PCB inductance around single-channel TVS

In order to reduce L3, the TVS ground pin is best connected directly to the coupled ground plane. Figure 2-8 shows the ground pad of TVS connected to the top ground plane. There are four splicing holes that connect the top grounding plane to the inner grounding plane. Depending on the number of layers and board design, these holes may be connected to multiple ground plane layers. The grounding case bolt position is also very close to the TVS grounding pad. A grounding scheme such as this would result in a very low ground impedance for L3.

Figure 2-8. Connect two layers of PCB- the top layer grounding plane to the middle layer grounding plane

Figure 2-8. Connect two layers of PCB- the top layer grounding plane to the middle layer grounding plane

Because of the package type, Figure 2-8 has nothing to do with certain types of TVS. TVS in a BGA package with ground pins surrounded by other pins need to connect an internal ground plane through a hole, preferably multiple coupled ground planes. Figure 2-9 shows a TVS with this grounding pin.

Figure 2-9. Ground the isolated ground pins in the BGA package

Figure 2-9. Ground the isolated ground pins in the BGA package

The holes need to be constructed to provide the smallest possible impedance. Maximizing the surface area of the GND crossing hole minimizes the impedance of the grounding path due to the skin effect. Therefore, the through hole pad diameter and through hole drilling diameter are made as large as possible, thus maximizing the surface area outside and inside the through hole surface. The ground plane should not be disconnected in the area near the GND crossing hole. If possible, connect the GND through-hole to the ground plane on multiple layers to minimize impedance. The GND pass hole should be filled with a non-conductive filler (such as resin) instead of a conductive filler, with the aim of preserving the surface area inside the pass hole created by the drilling hole. GND holes shall be plated on SMD pads. The gap between the GND crossing hole and the non-grounded plane (such as the power plane) should be kept to a minimum. This increases capacitance, which reduces impedance.

3. Conclusion

ESD protection can be successfully designed into the system as long as the appropriate technology is used. Following these ESD layout guide Outlines will ensure that TVS has the best conditions for dissipating ESD.

In SUMMARY:

• Control the impedance around TVS to dissipate ESD current IESD:

- Minimize the inductance between the ESD source and the grounding path through TVS

- If the design rules allow, place TVS near the connector

- Make the distance between the protected IC and the TVS far greater than the distance between the TVS and the connector.

- Do not use stumps between TVS and protected lines, route directly from ESD source to TVS

- It is important to minimize the inductance between the TVS and the ground

• Limit the impact of EMI on unprotected circuits:

- Do not lay unprotected circuits in the area between the ESD source and the TVS

- If the design rules allow, place TVS near the connector

- If possible, use straight line wiring between ESD source and TVS

- If corners must be used, curves should be preferred, with a maximum acceptable Angle of 45°

• Proper use of through-holes to maximize ESD dissipation with TVS:

- If possible, avoid using holes between ESD source and TVS

- If a pass hole is required between the ESD source and the protected IC, route directly from the ESD source to the TVS before using the pass hole

• Use an extremely low impedance grounding scheme:

- Connect the TVS ground pin directly to the ground plane of the same layer, ensuring that the ground plane has a nearby through-hole stitched to the adjacent internal ground plane

- Use as many ground planes as possible

- Use case screws, connect to PCB ground, place near TVS and ESD source (e.g., connector ground shield)

- Use large diameter and large drilled holes to reduce impedance